ചാനലിൻ്റെ നിലനിൽപ്പിന് FET നടത്താൻ കഴിയുമ്പോൾ D-FET 0 ഗേറ്റ് ബയസിലാണ്; ചാനൽ ഇല്ലാത്തപ്പോൾ E-FET 0 ഗേറ്റ് ബയസിലാണ്, FET നടത്താൻ കഴിയില്ല. ഈ രണ്ട് തരം FET-കൾക്ക് അവരുടേതായ സവിശേഷതകളും ഉപയോഗങ്ങളും ഉണ്ട്. പൊതുവേ, ഹൈ-സ്പീഡ്, ലോ-പവർ സർക്യൂട്ടുകളിൽ മെച്ചപ്പെടുത്തിയ FET വളരെ വിലപ്പെട്ടതാണ്; ഈ ഉപകരണം പ്രവർത്തിക്കുന്നു, ഇത് ഗേറ്റ് ബയസ് വോയുടെ ധ്രുവതയാണ്ltage ആൻഡ് ഡ്രെയിൻ അതേ വോൾട്ടേജ്, സർക്യൂട്ട് ഡിസൈനിൽ ഇത് കൂടുതൽ സൗകര്യപ്രദമാണ്.

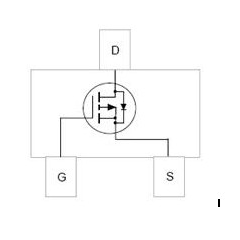

വികസിത മാർഗങ്ങൾ എന്ന് വിളിക്കപ്പെടുന്നവ: VGS = 0 ട്യൂബ് ഒരു കട്ട്-ഓഫ് അവസ്ഥയാണെങ്കിൽ, കൂടാതെ ശരിയായ VGS ആണെങ്കിൽ, ഭൂരിഭാഗം വാഹകരും ഗേറ്റിലേക്ക് ആകർഷിക്കപ്പെടുന്നു, അങ്ങനെ മേഖലയിലെ വാഹകരെ "വർദ്ധിപ്പിക്കുന്നു", ഒരു ചാലക ചാനൽ രൂപീകരിക്കുന്നു. n-ചാനൽ മെച്ചപ്പെടുത്തിയ MOSFET അടിസ്ഥാനപരമായി ഒരു ഇടത്-വലത് സമമിതി ടോപ്പോളജിയാണ്, ഇത് SiO2 ഫിലിം ഇൻസുലേഷൻ്റെ ഒരു ലെയറിൻ്റെ ജനറേഷനിലെ പി-ടൈപ്പ് അർദ്ധചാലകമാണ്. ഇത് പി-ടൈപ്പ് അർദ്ധചാലകത്തിൽ SiO2 ഫിലിമിൻ്റെ ഒരു ഇൻസുലേറ്റിംഗ് പാളി സൃഷ്ടിക്കുന്നു, തുടർന്ന് രണ്ട് ഉയർന്ന ഡോപ്പ് ഉള്ള N- തരം പ്രദേശങ്ങൾ വ്യാപിപ്പിക്കുന്നു.ഫോട്ടോലിത്തോഗ്രാഫി, കൂടാതെ എൻ-ടൈപ്പ് മേഖലയിൽ നിന്നുള്ള ലീഡ് ഇലക്ട്രോഡുകൾ, ഒന്ന് ഡ്രെയിനേജ് ഡിക്കും ഒന്ന് സോഴ്സ് എസ് നും. അലുമിനിയം ലോഹത്തിൻ്റെ ഒരു പാളി സോഴ്സിനും ഡ്രെയിനിനുമിടയിലുള്ള ഇൻസുലേറ്റിംഗ് ലെയറിൽ ഗേറ്റ് ജി ആയി പൂശുന്നു. എപ്പോൾ VGS = 0 V , ഡ്രെയിനിനും സ്രോതസ്സിനും ഇടയിൽ ബാക്ക്-ടു-ബാക്ക് ഡയോഡുകളുള്ള വളരെ കുറച്ച് ഡയോഡുകൾ ഉണ്ട്, D, S എന്നിവയ്ക്കിടയിലുള്ള വോൾട്ടേജ് D, S എന്നിവയ്ക്കിടയിൽ ഒരു വൈദ്യുതധാര ഉണ്ടാക്കുന്നില്ല. D, S എന്നിവയ്ക്കിടയിലുള്ള വൈദ്യുതധാര പ്രയോഗിച്ച വോൾട്ടേജ് മുഖേന രൂപപ്പെട്ടതല്ല.

ഗേറ്റ് വോൾട്ടേജ് ചേർക്കുമ്പോൾ, 0 < VGS < VGS(th), ഗേറ്റിനും സബ്സ്ട്രേറ്റിനുമിടയിൽ രൂപം കൊള്ളുന്ന കപ്പാസിറ്റീവ് വൈദ്യുത മണ്ഡലത്തിലൂടെ, ഗേറ്റിൻ്റെ താഴെയുള്ള പി-ടൈപ്പ് അർദ്ധചാലകത്തിലെ പോളിയോൺ ദ്വാരങ്ങൾ താഴേക്ക് തള്ളപ്പെടും. നെഗറ്റീവ് അയോണുകളുടെ നേർത്ത ശോഷണ പാളി പ്രത്യക്ഷപ്പെടുന്നു; അതേ സമയം, അത് ഉപരിതല പാളിയിലേക്ക് നീങ്ങാൻ അതിലെ ഒളിഗോണുകളെ ആകർഷിക്കും, പക്ഷേ ഡ്രെയിനും ഉറവിടവും ആശയവിനിമയം നടത്തുന്ന ഒരു ചാലക ചാനൽ രൂപീകരിക്കാൻ എണ്ണം പരിമിതവും അപര്യാപ്തവുമാണ്, അതിനാൽ ഡ്രെയിൻ കറൻ്റ് ഐഡി രൂപീകരിക്കുന്നതിന് ഇത് ഇപ്പോഴും പര്യാപ്തമല്ല. കൂടുതൽ വർദ്ധനവ് വിജിഎസ്, എപ്പോൾ വിജിഎസ് > VGS (th) (VGS (th) യെ ടേൺ-ഓൺ വോൾട്ടേജ് എന്ന് വിളിക്കുന്നു), കാരണം ഈ സമയത്ത് ഗേറ്റ് വോൾട്ടേജ് താരതമ്യേന ശക്തമായിരുന്നു, ഗേറ്റിന് താഴെയുള്ള പി-ടൈപ്പ് അർദ്ധചാലക ഉപരിതല പാളിയിൽ കൂടുതൽ ശേഖരിക്കുന്നു. ഇലക്ട്രോണുകൾ, നിങ്ങൾക്ക് ഒരു ട്രെഞ്ച്, ഡ്രെയിനേജ്, ആശയവിനിമയത്തിൻ്റെ ഉറവിടം എന്നിവ ഉണ്ടാക്കാം. ഈ സമയത്ത് ഡ്രെയിൻ ഉറവിട വോൾട്ടേജ് ചേർത്തിട്ടുണ്ടെങ്കിൽ, ഡ്രെയിൻ കറൻ്റ് ഐഡി രൂപീകരിക്കാം. ഗേറ്റിന് താഴെയായി രൂപപ്പെട്ട ചാലക ചാനലിലെ ഇലക്ട്രോണുകൾ, പി-ടൈപ്പ് അർദ്ധചാലക ധ്രുവത്തോടുകൂടിയ കാരിയർ ദ്വാരം വിപരീതമാണ്, അതിനാൽ ഇതിനെ ആൻ്റി-ടൈപ്പ് ലെയർ എന്ന് വിളിക്കുന്നു. VGS വർദ്ധിക്കുന്നത് തുടരുന്നതിനാൽ, ഐഡി വർദ്ധിക്കുന്നത് തുടരും. VGS = 0V-ൽ ID = 0, കൂടാതെ ഡ്രെയിൻ കറൻ്റ് സംഭവിക്കുന്നത് VGS > VGS(th) ന് ശേഷം മാത്രമാണ്, അതിനാൽ, ഇത്തരത്തിലുള്ള MOSFET-നെ മെച്ചപ്പെടുത്തൽ MOSFET എന്ന് വിളിക്കുന്നു.

ഡ്രെയിൻ കറൻ്റിലുള്ള VGS-ൻ്റെ നിയന്ത്രണ ബന്ധത്തെ iD = f(VGS(th))|VDS=const, ട്രാൻസ്ഫർ സ്വഭാവ കർവ് എന്ന് വിളിക്കുന്നു, കൂടാതെ ട്രാൻസ്ഫർ സ്വഭാവ വക്രത്തിൻ്റെ ചരിവിൻ്റെ വ്യാപ്തി, gm, ഗേറ്റ് ഉറവിട വോൾട്ടേജ് വഴി ഡ്രെയിൻ കറൻ്റ് നിയന്ത്രണം പ്രതിഫലിപ്പിക്കുന്നു. gm ൻ്റെ കാന്തിമാനം mA/V ആണ്, അതിനാൽ gm-നെ ട്രാൻസ്കണ്ടക്റ്റൻസ് എന്നും വിളിക്കുന്നു.