അർദ്ധചാലക വ്യവസായത്തിലെ ഏറ്റവും അടിസ്ഥാന ഘടകങ്ങളിലൊന്നാണ് MOSFET. ഇലക്ട്രോണിക് സർക്യൂട്ടുകളിൽ, MOSFET സാധാരണയായി പവർ ആംപ്ലിഫയർ സർക്യൂട്ടുകളിലോ സ്വിച്ചിംഗ് പവർ സപ്ലൈ സർക്യൂട്ടുകളിലോ ഉപയോഗിക്കുന്നു, ഇത് വ്യാപകമായി ഉപയോഗിക്കപ്പെടുന്നു. താഴെ,ഒലുകെയ്MOSFET-ൻ്റെ പ്രവർത്തന തത്വത്തിൻ്റെ വിശദമായ വിശദീകരണം നൽകുകയും MOSFET-ൻ്റെ ആന്തരിക ഘടന വിശകലനം ചെയ്യുകയും ചെയ്യും.

എന്താണ്മോസ്ഫെറ്റ്

MOSFET, മെറ്റൽ ഓക്സൈഡ് സെമികണ്ടക്ടർ ഫയൽഡ് ഇഫക്റ്റ് ട്രാൻസിസ്റ്റർ (MOSFET). അനലോഗ് സർക്യൂട്ടുകളിലും ഡിജിറ്റൽ സർക്യൂട്ടുകളിലും വ്യാപകമായി ഉപയോഗിക്കാവുന്ന ഒരു ഫീൽഡ് ഇഫക്റ്റ് ട്രാൻസിസ്റ്ററാണിത്. അതിൻ്റെ "ചാനലിൻ്റെ" (വർക്കിംഗ് കാരിയർ) ധ്രുവീയ വ്യത്യാസം അനുസരിച്ച്, അതിനെ രണ്ട് തരങ്ങളായി തിരിക്കാം: "N-type", "P-type", അവയെ പലപ്പോഴും NMOS എന്നും PMOS എന്നും വിളിക്കുന്നു.

MOSFET പ്രവർത്തന തത്വം

വർക്കിംഗ് മോഡ് അനുസരിച്ച് MOSFET നെ എൻഹാൻസ്മെൻ്റ് തരമായും ശോഷണ തരമായും വിഭജിക്കാം. ബയസ് വോൾട്ടേജ് പ്രയോഗിക്കാതിരിക്കുകയും കോൺ ഇല്ലാതിരിക്കുകയും ചെയ്യുമ്പോൾ മെച്ചപ്പെടുത്തൽ തരം MOSFET സൂചിപ്പിക്കുന്നുഡക്റ്റീവ് ചാനൽ. ബയസ് വോൾട്ടേജ് പ്രയോഗിക്കാത്തപ്പോൾ ഡിപ്ലിഷൻ തരം MOSFET സൂചിപ്പിക്കുന്നു. ഒരു ചാലക ചാനൽ ദൃശ്യമാകും.

യഥാർത്ഥ ആപ്ലിക്കേഷനുകളിൽ, N-ചാനൽ മെച്ചപ്പെടുത്തൽ തരവും P-ചാനൽ മെച്ചപ്പെടുത്തൽ തരവും MOSFET-കൾ മാത്രമേയുള്ളൂ. NMOSFET-കൾക്ക് ചെറിയ സംസ്ഥാന പ്രതിരോധം ഉള്ളതിനാൽ നിർമ്മിക്കാൻ എളുപ്പമുള്ളതിനാൽ, യഥാർത്ഥ ആപ്ലിക്കേഷനുകളിൽ PMOS-നേക്കാൾ NMOS സാധാരണമാണ്.

എൻഹാൻസ്മെൻ്റ് മോഡ് MOSFET

എൻഹാൻസ്മെൻ്റ് മോഡ് മോസ്ഫെറ്റിൻ്റെ ഡ്രെയിൻ ഡിക്കും സോഴ്സ് എസിനും ഇടയിൽ രണ്ട് ബാക്ക്-ടു-ബാക്ക് പിഎൻ ജംഗ്ഷനുകളുണ്ട്. ഗേറ്റ്-സോഴ്സ് വോൾട്ടേജ് VGS=0 ആയിരിക്കുമ്പോൾ, ഡ്രെയിൻ-സോഴ്സ് വോൾട്ടേജ് VDS ചേർത്താലും, എല്ലായ്പ്പോഴും ഒരു റിവേഴ്സ്-ബയേസ്ഡ് സ്റ്റേറ്റിൽ ഒരു PN ജംഗ്ഷൻ ഉണ്ടാകും, കൂടാതെ ഡ്രെയിനിനും ഉറവിടത്തിനും ഇടയിൽ ഒരു ചാലക ചാനലും ഇല്ല (നിലവിലെ ഒഴുക്ക് ഇല്ല. ). അതിനാൽ, ഈ സമയത്ത് ഡ്രെയിൻ കറൻ്റ് ID=0.

ഈ സമയത്ത്, ഗേറ്റിനും ഉറവിടത്തിനും ഇടയിൽ ഒരു ഫോർവേഡ് വോൾട്ടേജ് ചേർത്തിട്ടുണ്ടെങ്കിൽ. അതായത്, VGS>0, അപ്പോൾ ഗേറ്റ് ഇലക്ട്രോഡിനും സിലിക്കൺ സബ്സ്ട്രേറ്റിനും ഇടയിലുള്ള SiO2 ഇൻസുലേറ്റിംഗ് ലെയറിൽ പി-ടൈപ്പ് സിലിക്കൺ സബ്സ്ട്രേറ്റുമായി വിന്യസിച്ചിരിക്കുന്ന ഗേറ്റുള്ള ഒരു വൈദ്യുത മണ്ഡലം സൃഷ്ടിക്കപ്പെടും. ഓക്സൈഡ് പാളി ഇൻസുലേറ്റിംഗ് ആയതിനാൽ, ഗേറ്റിൽ പ്രയോഗിക്കുന്ന വോൾട്ടേജ് VGS ന് കറൻ്റ് ഉത്പാദിപ്പിക്കാൻ കഴിയില്ല. ഓക്സൈഡ് പാളിയുടെ ഇരുവശത്തും ഒരു കപ്പാസിറ്റർ സൃഷ്ടിക്കപ്പെടുന്നു, കൂടാതെ VGS തത്തുല്യമായ സർക്യൂട്ട് ഈ കപ്പാസിറ്റർ (കപ്പാസിറ്റർ) ചാർജ് ചെയ്യുന്നു. ഗേറ്റിൻ്റെ പോസിറ്റീവ് വോൾട്ടേജാൽ ആകർഷിക്കപ്പെടുന്ന VGS സാവധാനം ഉയരുമ്പോൾ ഒരു വൈദ്യുത മണ്ഡലം സൃഷ്ടിക്കുക. ഈ കപ്പാസിറ്ററിൻ്റെ (കപ്പാസിറ്റർ) മറുവശത്ത് ധാരാളം ഇലക്ട്രോണുകൾ അടിഞ്ഞുകൂടുകയും ഡ്രെയിനിൽ നിന്ന് ഉറവിടത്തിലേക്ക് ഒരു N-തരം ചാലക ചാനൽ സൃഷ്ടിക്കുകയും ചെയ്യുന്നു. ട്യൂബിൻ്റെ ടേൺ-ഓൺ വോൾട്ടേജ് VT-യെ VGS കവിയുമ്പോൾ (സാധാരണയായി ഏകദേശം 2V), N-ചാനൽ ട്യൂബ് പ്രവർത്തിക്കാൻ തുടങ്ങുന്നു, ഇത് ഒരു ഡ്രെയിൻ കറൻ്റ് ഐഡി സൃഷ്ടിക്കുന്നു. ചാനൽ ആദ്യം ടേൺ-ഓൺ വോൾട്ടേജ് സൃഷ്ടിക്കാൻ തുടങ്ങുമ്പോൾ ഞങ്ങൾ ഗേറ്റ്-സോഴ്സ് വോൾട്ടേജ് എന്ന് വിളിക്കുന്നു. VT എന്ന് പൊതുവെ പ്രകടിപ്പിക്കുന്നു.

ഗേറ്റ് വോൾട്ടേജ് VGS ൻ്റെ വലുപ്പം നിയന്ത്രിക്കുന്നത് വൈദ്യുത മണ്ഡലത്തിൻ്റെ ശക്തിയോ ബലഹീനതയോ മാറ്റുന്നു, കൂടാതെ ഡ്രെയിൻ കറൻ്റ് ഐഡിയുടെ വലുപ്പം നിയന്ത്രിക്കുന്നതിൻ്റെ ഫലം കൈവരിക്കാൻ കഴിയും. കറൻ്റ് നിയന്ത്രിക്കാൻ ഇലക്ട്രിക് ഫീൽഡുകൾ ഉപയോഗിക്കുന്ന MOSFET കളുടെ ഒരു പ്രധാന സവിശേഷത കൂടിയാണിത്, അതിനാൽ അവയെ ഫീൽഡ് ഇഫക്റ്റ് ട്രാൻസിസ്റ്ററുകൾ എന്നും വിളിക്കുന്നു.

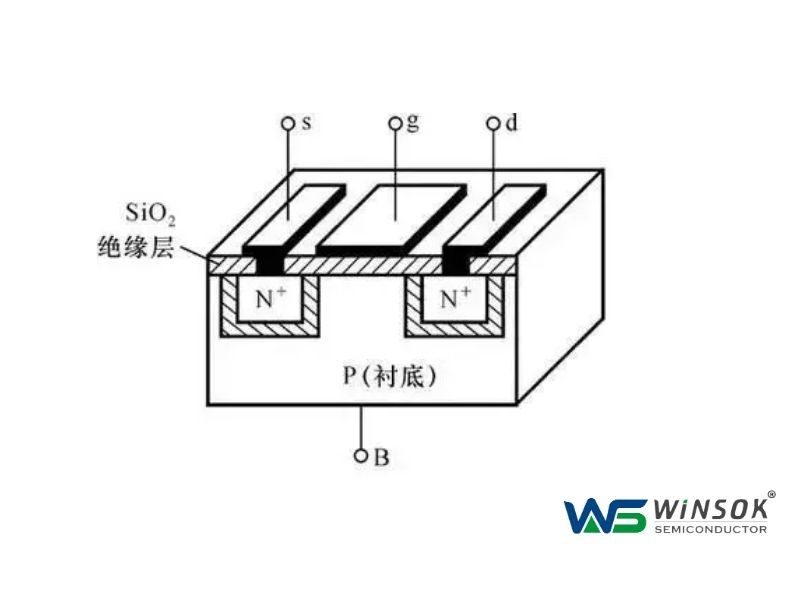

MOSFET ആന്തരിക ഘടന

കുറഞ്ഞ അശുദ്ധി സാന്ദ്രതയുള്ള പി-ടൈപ്പ് സിലിക്കൺ സബ്സ്ട്രേറ്റിൽ, ഉയർന്ന അശുദ്ധി സാന്ദ്രതയുള്ള രണ്ട് N+ മേഖലകൾ നിർമ്മിക്കുന്നു, കൂടാതെ രണ്ട് ഇലക്ട്രോഡുകൾ ലോഹ അലുമിനിയത്തിൽ നിന്ന് വലിച്ചെടുത്ത് യഥാക്രമം ഡ്രെയിൻ d ആയും ഉറവിടമായും പ്രവർത്തിക്കുന്നു. അർദ്ധചാലക ഉപരിതലം വളരെ നേർത്ത സിലിക്കൺ ഡൈ ഓക്സൈഡ് (SiO2) ഇൻസുലേറ്റിംഗ് പാളി കൊണ്ട് മൂടിയിരിക്കുന്നു, കൂടാതെ ഗേറ്റ് g ആയി പ്രവർത്തിക്കുന്നതിന് ഡ്രെയിനിനും ഉറവിടത്തിനും ഇടയിലുള്ള ഇൻസുലേറ്റിംഗ് ലെയറിൽ ഒരു അലുമിനിയം ഇലക്ട്രോഡ് സ്ഥാപിക്കുന്നു. ഒരു ഇലക്ട്രോഡ് ബിയും അടിവസ്ത്രത്തിൽ വലിച്ചെടുക്കുന്നു, ഇത് ഒരു N-ചാനൽ മെച്ചപ്പെടുത്തൽ മോഡ് MOSFET രൂപീകരിക്കുന്നു. പി-ചാനൽ എൻഹാൻസ്മെൻ്റ്-ടൈപ്പ് മോസ്ഫെറ്റുകളുടെ ആന്തരിക രൂപീകരണത്തിനും ഇത് ബാധകമാണ്.

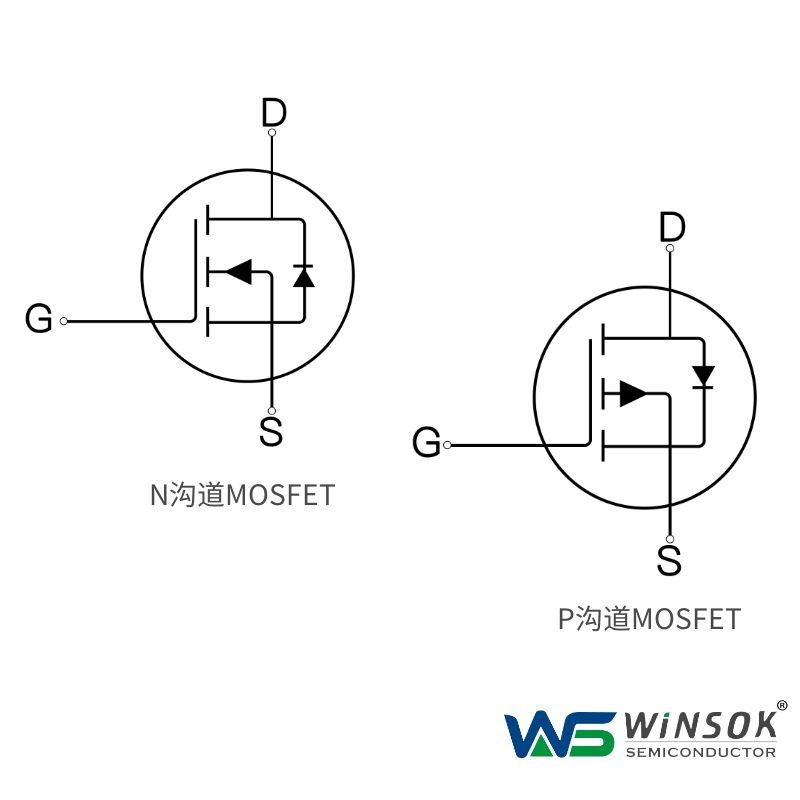

N-channel MOSFET, P-channel MOSFET സർക്യൂട്ട് ചിഹ്നങ്ങൾ

മുകളിലെ ചിത്രം MOSFET ൻ്റെ സർക്യൂട്ട് ചിഹ്നം കാണിക്കുന്നു. ചിത്രത്തിൽ, D എന്നത് ഡ്രെയിനേജ് ആണ്, S ആണ് ഉറവിടം, G എന്നത് ഗേറ്റ് ആണ്, നടുവിലുള്ള അമ്പടയാളം അടിവസ്ത്രത്തെ പ്രതിനിധീകരിക്കുന്നു. അമ്പടയാളം അകത്തേക്ക് ചൂണ്ടുകയാണെങ്കിൽ, അത് ഒരു N-ചാനൽ MOSFET യെ സൂചിപ്പിക്കുന്നു, അമ്പ് പുറത്തേക്ക് ചൂണ്ടുകയാണെങ്കിൽ, അത് P-ചാനൽ MOSFET സൂചിപ്പിക്കുന്നു.

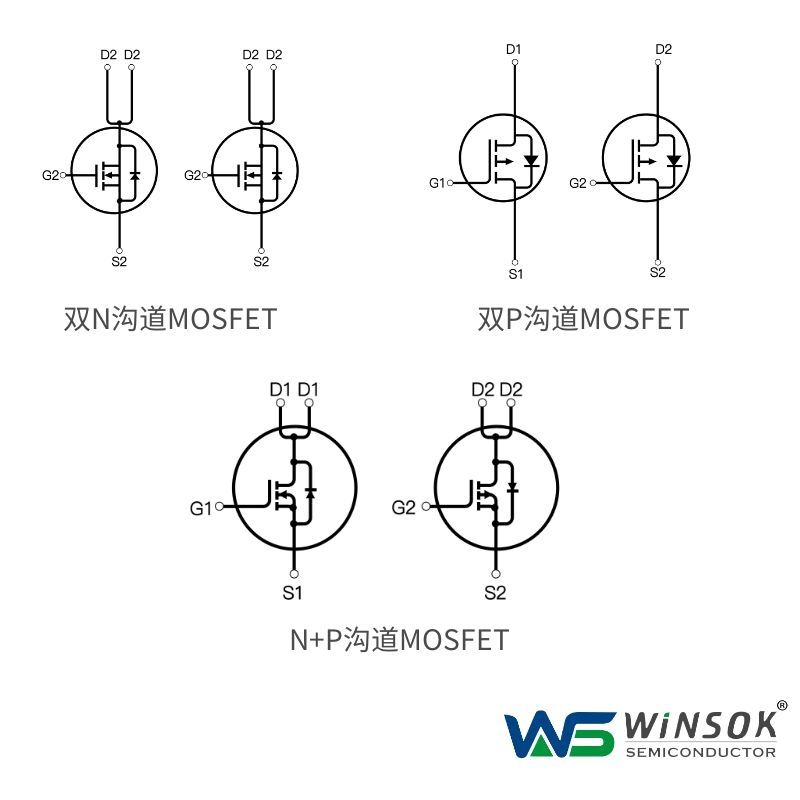

ഡ്യുവൽ N-ചാനൽ MOSFET, ഡ്യുവൽ P-ചാനൽ MOSFET, N+P-ചാനൽ MOSFET സർക്യൂട്ട് ചിഹ്നങ്ങൾ

വാസ്തവത്തിൽ, MOSFET നിർമ്മാണ പ്രക്രിയയിൽ, ഫാക്ടറി വിടുന്നതിന് മുമ്പ് അടിവസ്ത്രം ഉറവിടവുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു. അതിനാൽ, സിംബോളജി നിയമങ്ങളിൽ, അഴുക്കും ഉറവിടവും വേർതിരിച്ചറിയാൻ അടിവസ്ത്രത്തെ പ്രതിനിധീകരിക്കുന്ന അമ്പടയാള ചിഹ്നവും ഉറവിടവുമായി ബന്ധിപ്പിച്ചിരിക്കണം. MOSFET ഉപയോഗിക്കുന്ന വോൾട്ടേജിൻ്റെ പോളാരിറ്റി നമ്മുടെ പരമ്പരാഗത ട്രാൻസിസ്റ്ററിന് സമാനമാണ്. N-ചാനൽ ഒരു NPN ട്രാൻസിസ്റ്ററിന് സമാനമാണ്. ഡ്രെയിൻ ഡി പോസിറ്റീവ് ഇലക്ട്രോഡുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു, ഉറവിടം എസ് നെഗറ്റീവ് ഇലക്ട്രോഡുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു. ഗേറ്റ് ജിക്ക് പോസിറ്റീവ് വോൾട്ടേജ് ഉള്ളപ്പോൾ, ഒരു ചാലക ചാനൽ രൂപപ്പെടുകയും N-ചാനൽ MOSFET പ്രവർത്തിക്കാൻ തുടങ്ങുകയും ചെയ്യുന്നു. അതുപോലെ, പി-ചാനൽ ഒരു പിഎൻപി ട്രാൻസിസ്റ്ററിന് സമാനമാണ്. ഡ്രെയിൻ ഡി നെഗറ്റീവ് ഇലക്ട്രോഡുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു, ഉറവിടം എസ് പോസിറ്റീവ് ഇലക്ട്രോഡുമായി ബന്ധിപ്പിച്ചിരിക്കുന്നു, ഗേറ്റ് ജിക്ക് നെഗറ്റീവ് വോൾട്ടേജ് ഉള്ളപ്പോൾ, ഒരു ചാലക ചാനൽ രൂപപ്പെടുകയും പി-ചാനൽ മോസ്ഫെറ്റ് പ്രവർത്തിക്കാൻ തുടങ്ങുകയും ചെയ്യുന്നു.

MOSFET സ്വിച്ചിംഗ് നഷ്ടത്തിൻ്റെ തത്വം

അത് NMOS ആയാലും PMOS ആയാലും, അത് ഓണാക്കിയതിന് ശേഷം ഒരു ചാലക ആന്തരിക പ്രതിരോധം ഉണ്ടാകുന്നു, അതിനാൽ ഈ ആന്തരിക പ്രതിരോധത്തിൽ കറൻ്റ് ഊർജ്ജം ചെലവഴിക്കും. ഉപഭോഗം ചെയ്യുന്ന ഊർജ്ജത്തിൻ്റെ ഈ ഭാഗത്തെ ചാലക ഉപഭോഗം എന്ന് വിളിക്കുന്നു. ഒരു ചെറിയ ചാലക ആന്തരിക പ്രതിരോധം ഉള്ള ഒരു MOSFET തിരഞ്ഞെടുക്കുന്നത് ചാലക ഉപഭോഗം ഫലപ്രദമായി കുറയ്ക്കും. ലോ-പവർ MOSFET-കളുടെ നിലവിലെ ആന്തരിക പ്രതിരോധം സാധാരണയായി പതിനായിരക്കണക്കിന് മില്ലിഓം ആണ്, കൂടാതെ നിരവധി മില്ലിഓമുകളും ഉണ്ട്.

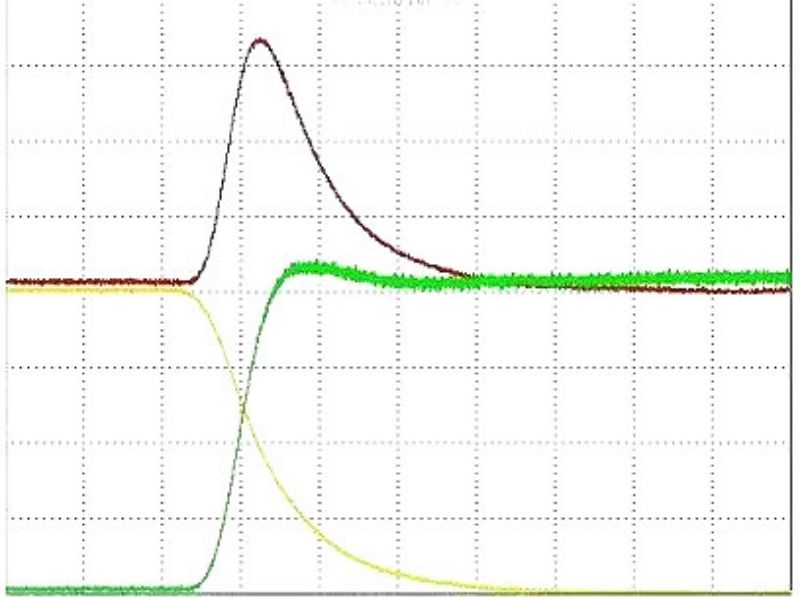

MOS ഓൺ ചെയ്യുകയും അവസാനിപ്പിക്കുകയും ചെയ്യുമ്പോൾ, അത് ഒരു തൽക്ഷണം തിരിച്ചറിയാൻ പാടില്ല. MOS ൻ്റെ ഇരുവശത്തുമുള്ള വോൾട്ടേജിൽ ഫലപ്രദമായ കുറവുണ്ടാകും, അതിലൂടെ ഒഴുകുന്ന വൈദ്യുതധാരയിൽ വർദ്ധനവുണ്ടാകും. ഈ കാലയളവിൽ, MOSFET ൻ്റെ നഷ്ടം വോൾട്ടേജിൻ്റെയും കറൻ്റിൻ്റെയും ഉൽപ്പന്നമാണ്, ഇത് സ്വിച്ചിംഗ് നഷ്ടമാണ്. പൊതുവായി പറഞ്ഞാൽ, സ്വിച്ചിംഗ് നഷ്ടങ്ങൾ ചാലക നഷ്ടത്തേക്കാൾ വളരെ വലുതാണ്, കൂടാതെ സ്വിച്ചിംഗ് ആവൃത്തി വേഗത്തിൽ മാറുമ്പോൾ നഷ്ടം വർദ്ധിക്കും.

ചാലകത്തിൻ്റെ നിമിഷത്തിൽ വോൾട്ടേജിൻ്റെയും വൈദ്യുതധാരയുടെയും ഉൽപ്പന്നം വളരെ വലുതാണ്, ഇത് വളരെ വലിയ നഷ്ടത്തിന് കാരണമാകുന്നു. സ്വിച്ചിംഗ് നഷ്ടം രണ്ട് തരത്തിൽ കുറയ്ക്കാം. ഒന്ന്, സ്വിച്ചിംഗ് സമയം കുറയ്ക്കുക എന്നതാണ്, ഓരോ ടേൺ-ഓൺ സമയത്തും നഷ്ടം ഫലപ്രദമായി കുറയ്ക്കാൻ കഴിയും; മറ്റൊന്ന് സ്വിച്ചിംഗ് ഫ്രീക്വൻസി കുറയ്ക്കുക എന്നതാണ്, ഇത് യൂണിറ്റ് സമയത്തിന് സ്വിച്ചുകളുടെ എണ്ണം കുറയ്ക്കും.

MOSFET-ൻ്റെ പ്രവർത്തന തത്വ ഡയഗ്രം, MOSFET-ൻ്റെ ആന്തരിക ഘടനയുടെ വിശകലനം എന്നിവയുടെ വിശദമായ വിശദീകരണമാണ് മുകളിൽ നൽകിയിരിക്കുന്നത്. MOSFET-നെ കുറിച്ച് കൂടുതലറിയാൻ, നിങ്ങൾക്ക് MOSFET സാങ്കേതിക പിന്തുണ നൽകാൻ OLUKEY-യെ സമീപിക്കാൻ സ്വാഗതം!